At the IEEE International Electron Device Meeting (IEDM) earlier this month, Taiwan Semiconductor Manufacturing Company (TSMC) provided further insights into its upcoming N2 (2nm-class) process node. This next-generation technology, set to begin mass production in the second half of 2025, promises significant improvements in performance, energy efficiency, and transistor density.

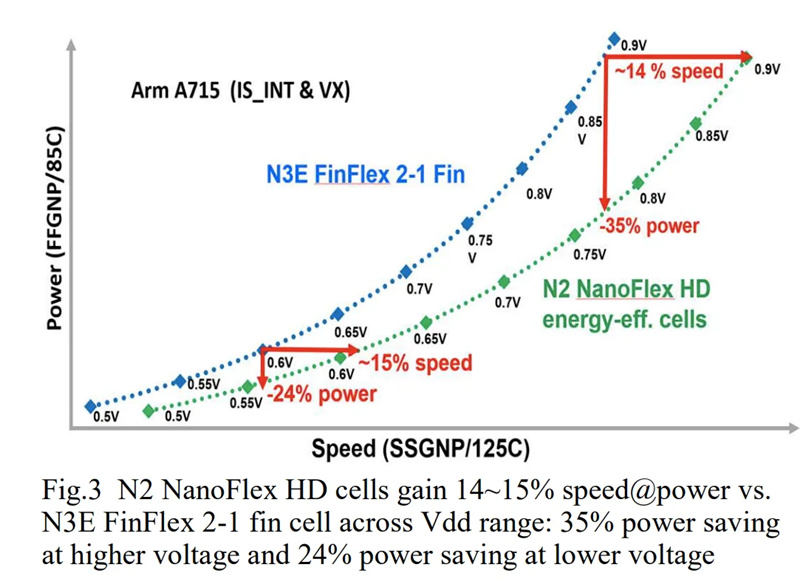

TSMC's N2 technology boasts up to 35% greater energy efficiency or 15% faster performance compared to the current 3nm process, while also achieving a 15% increase in transistor density. These advances are primarily driven by the implementation of TSMC’s gate-all-around (GAA) nanosheet transistors, which are optimized by N2 NanoFlex design-technology co-optimization (DTCO), along with other process refinements.

Breakthroughs in Transistor Design and Performance

The key innovation behind N2’s enhanced performance lies in the GAA nanosheet transistors, which allow designers to adjust the width of the nanosheets to optimize power efficiency and performance. Unlike FinFETs, which rely on multiple vertical fins to adjust device characteristics, the GAA nanosheets offer more flexibility by enabling variations in the width of individual nanosheets, allowing for a more nuanced optimization of devices.

In terms of power efficiency, N2's nanosheet transistors perform exceptionally well at low supply voltages ranging from 0.5V to 0.6V. At these voltages, the technology provides a 20% boost in clock speeds and reduces standby power consumption by as much as 75%. This makes N2 particularly well-suited for energy-efficient processors in high-density logic applications.

SRAM Advancements and Design Flexibility

Another major breakthrough introduced with the N2 process is in SRAM (Static Random Access Memory) technology. TSMC's N2 technology achieves a record-breaking 2nm SRAM density of approximately 38 megabits per square millimeter (Mb/mm²), an 11% improvement over the N3 process. This improvement is attributed to the superior transistor architecture and design flexibility provided by the GAA nanosheet transistors, which significantly enhance SRAM scalability—a challenge faced by previous cutting-edge nodes.

Additionally, the integration of N2 NanoFlex DTCO and multi-threshold voltage (multi-Vt) options enables greater design flexibility, allowing for the creation of energy-efficient processors that also boast high logic density. This flexibility is especially beneficial for high-performance computing (HPC) applications, where performance and power efficiency are critical.

Improved Process Efficiency and Yield

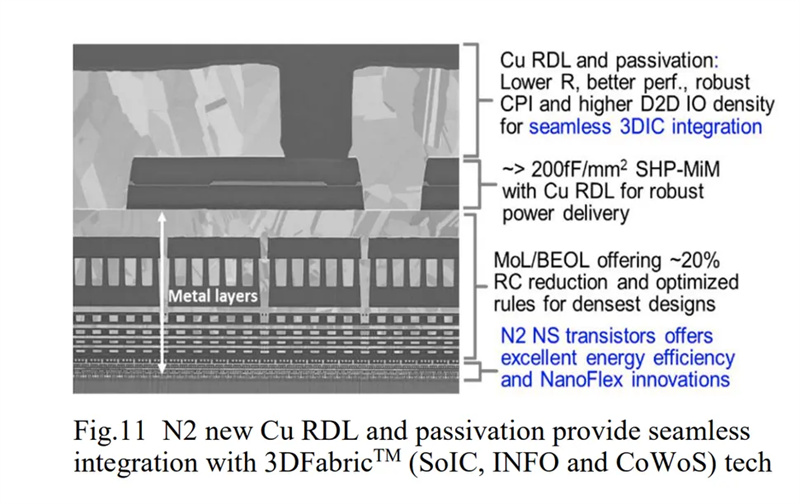

TSMC's new process node also brings several process enhancements. The middle-of-line (MoL), back-end-of-line (BEOL), and far-BEOL wiring have all been optimized to reduce resistance by 20%, improving performance efficiency. Notably, TSMC’s N2 MoL now uses barrier-free tungsten wiring, which reduces vertical gate contact resistance by 55%, boosting the frequency of ring oscillators by around 6.2%. The company has also implemented a single EUV exposure pass followed by a single etch step for the first metal layer (M1), streamlining the process and reducing complexity.

Industry sources indicate that TSMC's trial production yield for its 2nm node has already surpassed 60%, exceeding expectations. This strong yield rate signals a successful path toward mass production in 2025.

Looking Forward

TSMC's N2 process represents a significant leap forward in semiconductor technology, with its combination of cutting-edge transistor design, superior energy efficiency, and enhanced design flexibility positioning it as a critical technology for future high-performance applications. As the company prepares for mass production, N2 is poised to drive advancements in industries ranging from high-performance computing to telecommunications, healthcare, and beyond. With N2, TSMC aims to continue its leadership in the semiconductor industry, setting new standards for performance, efficiency, and scalability.

+86 191 9627 2716

+86 181 7379 0595

8:30 a.m. to 5:30 p.m., Monday to Friday